# Radiation Hardened FPGA Technology for Space Applications MAPLD 2008

#### Leonard Rockett<sup>1</sup>, <u>Dinu Patel<sup>1</sup></u>, Steven Danziger<sup>1</sup>, J.J. Wang<sup>2</sup>, and Brian Cronquist<sup>2</sup> Frank Hawley<sup>2</sup>

<sup>1</sup>BAE Systems, 9300 Wellington Road, Manassas, VA 20110-4122 <sup>2</sup>Actel Corporation, 2061 Stierlin Court, Mountain View, CA 94043-4655

October 17, 2008

RHAX250-S effort supported by the Defense Threat Reduction Agency

## **RHFPGA Programs at BAE SYSTEMS**

- RH FPGA Product Roadmap

- RH FPGA Technologies

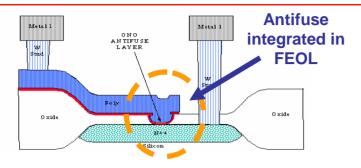

- ONO (Oxide Nitride Oxide Antifuse)

- M2M (Metal to Metal Antifuse)

- RH FPGA Program Status Review

- Reinstall RH1020/RH1280 FPGA

- RHAX FPGA Demonstration and Qualification Program

- Summary and Outlook

- Rad Hard FPGA Product • Heritage: Actel ONO RH1280 and RH1020 **Re-install**  Anti-fuse technology, non-volatile Past in progress 0.8µm RH CMOS, 5V Supply In production since 1996, over 25,000 shipped M2M Anti-fuse Technology: • 250K-gate (RHAX250-S) Entry Vehicle Present • RH15 CMOS, 1.5V Core / 3.3V I/O Flight Orders in 2009 • ≥3M-gate, re-programmable, non-volatile

- **Future**

- Radiation Hardened, high speed

- RH15 CMOS, 1.5V Core / 3.3V I/O

- Projected qualification starts in 2009

**BAE Supporting RHFPGA Needs for RHOC requirements**

# ONO RHFPGA Program BAE SYSTEMS

- ONO technology : (0.8 micron features)

- Flight qualified production (with build-out inventory) [1996-2002]

- Process line re-tooled to support 250 and 150 nm technology nodes on 150mm wafers

- ONO technology now reinstalled in modernized foundry to restart FPGA & PROM product to supply continued demand [2007- ]

$\succ$  Used same design data  $\Rightarrow$  same form, fit, and function as product built previously

Keeping same 0.8 micron features

# **PROM Features**

- Features and Capabilities

- Low voltage version: 32K x 8, 3.3V

- SMD #5962G02502

- High voltage version: 32K x 8, 5V

- SMD #5962R96891

- Latch-up immune

- Total dose: 200 Krad(Si)

- Schedule and Status

- In Production

- Delivery in 8 weeks

### ONO Rad Hard FPGA Technology Features

#### Features

- Guaranteed Total Dose Radiation Capability

- Low Single Event Upset Susceptibility

- High Dose Rate Survivability

- Latch-Up Immunity Guaranteed

- QML Qualified Devices

- Commercial Devices Available for Prototyping and Pre-Production Requirements

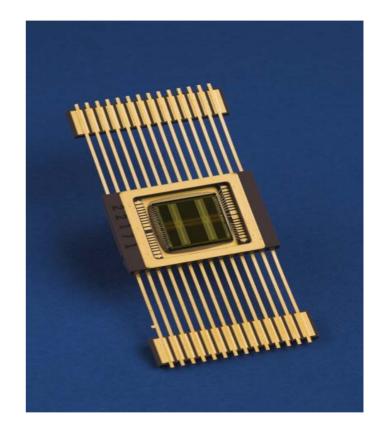

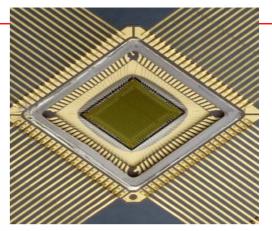

- Gate Capacities of 2,000 and 8,000 Gate Array Gates

- More Design Flexibility than Custom ASICs

- Significantly Greater Densities than Discrete Logic Devices

- Replaces up to 200 TTL Packages

- Design Library with over 500 Macro Functions

- Single-Module Sequential Functions

- Wide-Input Combinatorial Functions

- Up to Two High-Speed, Low-Skew Clock Networks

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 50 MHz

- Non-Volatile, User Programmable Devices

- Fabricated in 0.8 µ Epitaxial Bulk CMOS Process

- Unique In-System Diagnostic and Verification Capability with Silicon Explorer

|  | Product | Family | Profile |

|--|---------|--------|---------|

|--|---------|--------|---------|

| Device                                                                                                                                       | RH1020                              | RH1280                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|

| Capacity<br>System Gates<br>Gate Array Equivalent Gates<br>PLD Equivalent Gates<br>TTL Equivalent Packages<br>20-Pin PAL Equivalent Packages | 3,000<br>2,000<br>6,000<br>50<br>20 | 12,000<br>8,000<br>20,000<br>200<br>80 |

| Logic Modules<br>S-Modules<br>C-Modules                                                                                                      | 547<br>0<br>547                     | 1,232<br>624<br>608                    |

| Flip-Flops (Maximum)                                                                                                                         | 273                                 | 998                                    |

| Routing Resources<br>Horizontal Tracks/Channel<br>Vertical Tracks/Channel<br>PLICE Antifuse Elements                                         | 22<br>13<br>186,000                 | 35<br>15<br>750,000                    |

| User I/Os (Maximum)                                                                                                                          | 69                                  | 140                                    |

| Packages (by Pin Count)<br>Ceramic Quad Flat Pack (CQFP)                                                                                     | 84                                  | 172                                    |

## **ONO Rad Hard FPGA Radiation Features BAE SYSTEMS**

#### **Radiation Specifications**

Table 1-2 • Radiation Specifications<sup>1, 2</sup>

| Symbol            | Characteristics                  | Conditions                 | Min.    | Max.  | Units                      |

|-------------------|----------------------------------|----------------------------|---------|-------|----------------------------|

| RTD               | Total Dose                       |                            |         | 300 k | Rad (Si)                   |

| SEL               | Single Event Latch-Up            | –55°C ≤ $T_{case}$ ≤ 125°C |         | 0     | Fails/Device-Day           |

| SEU1 <sup>3</sup> | Single Event Upset for S-modules | –55°C ≤ $T_{case}$ ≤ 125°C |         | 1E-6  | Upsets/Bit-Day             |

| SEU2 <sup>3</sup> | Single Event Upset for C-modules | –55°C ≤ $T_{case}$ ≤ 125°C |         | 1E-7  | Upsets/Bit-Day             |

| SEU3 <sup>3</sup> | Single Event Fuse Rupture        | –55°C ≤ $T_{case}$ ≤ 125°C |         | <1    | FIT (Fails/Device/1E9 Hrs) |

| RNF               | Neutron Fluence                  |                            | >1 E+12 |       | N/cm <sup>2</sup>          |

#### Notes:

- 1. Measured at room temperature unless otherwise stated.

- 2. Device electrical characteristics are guaranteed for post-irradiation levels at worst-case conditions.

- 10% worst-case particle environment, geosynchronous orbit, 0.025' of aluminum shielding. Specification set using the CREME code upset rate calculation method with a 2 μ epi thickness.

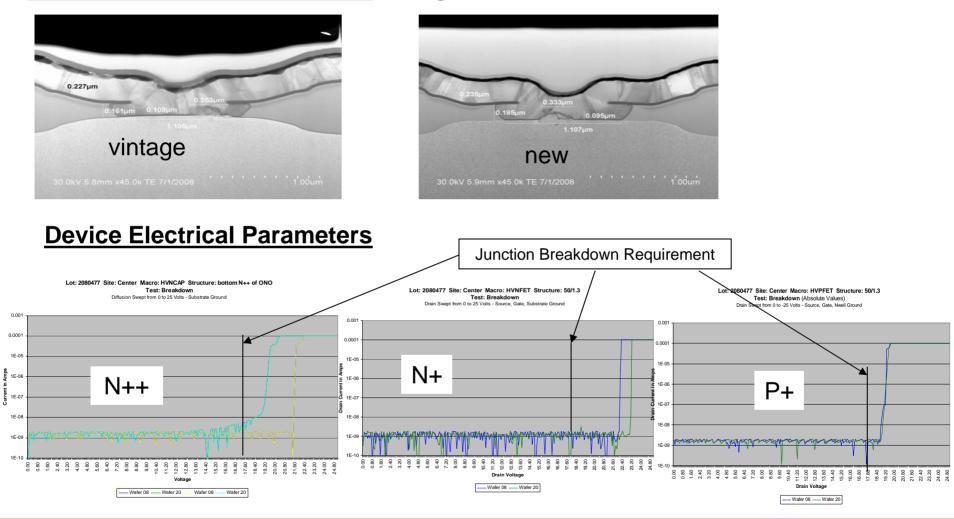

## **RH ONO Technology Process Data**

**BAE SYSTEMS**

#### **ONO Anti-fuse Cross sections - Programmed**

**RH ONO Re-installed Technology Meets Device Parameters Requirements**

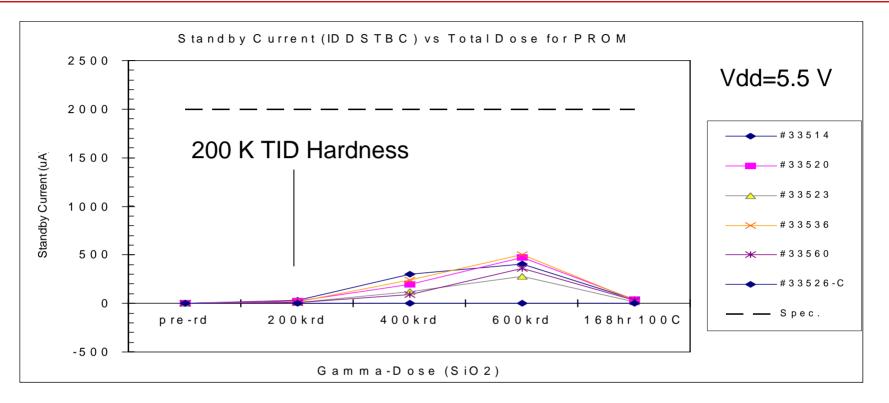

# RH ONO Technology TID Data - PROM BAE SYSTEMS

Active current, VIL, VIH, Access time and chip enable time all remain stable through 600 Krd

#### **RH PROM Exceeds 200 Krad TID Requirements**

# **ONO RHFPGA Program Status**

- Successfully reinstalled ONO process technology

- Flight-qualified PROM production restarted

- RH1280B prototype hardware successfully delivered, flight hardware in qualification.

- BAE acquired license from Actel to produce, market and sell RH1280 FPGA's

**BAE SYSTEMS**

- SEGR completed successfully, TID testing in progress

- RH1020 FPGA build underway for prototype and flight Qualification

ONO FPGA Flight Hardware in Production Orders being taken for shipments in 2008

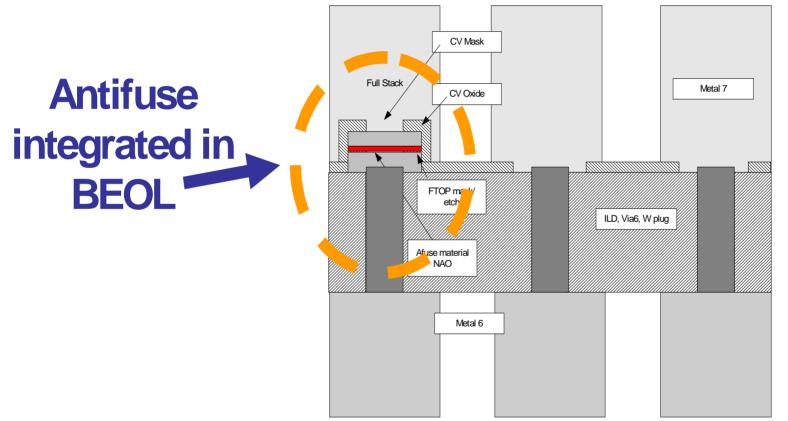

# **Metal to Metal Antifuse Based FPGA's**

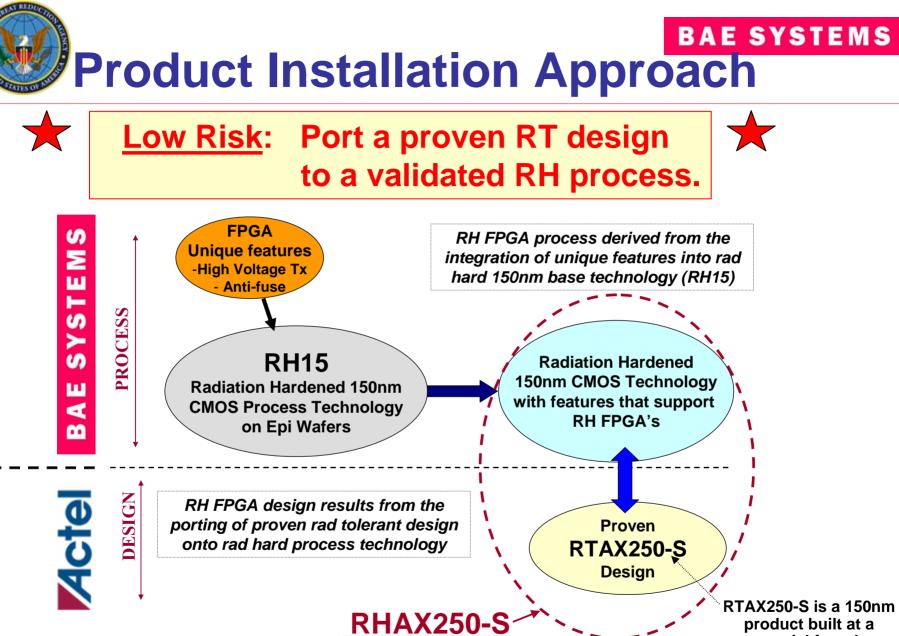

product built at a commercial foundry on non-epi substrates.

Actel

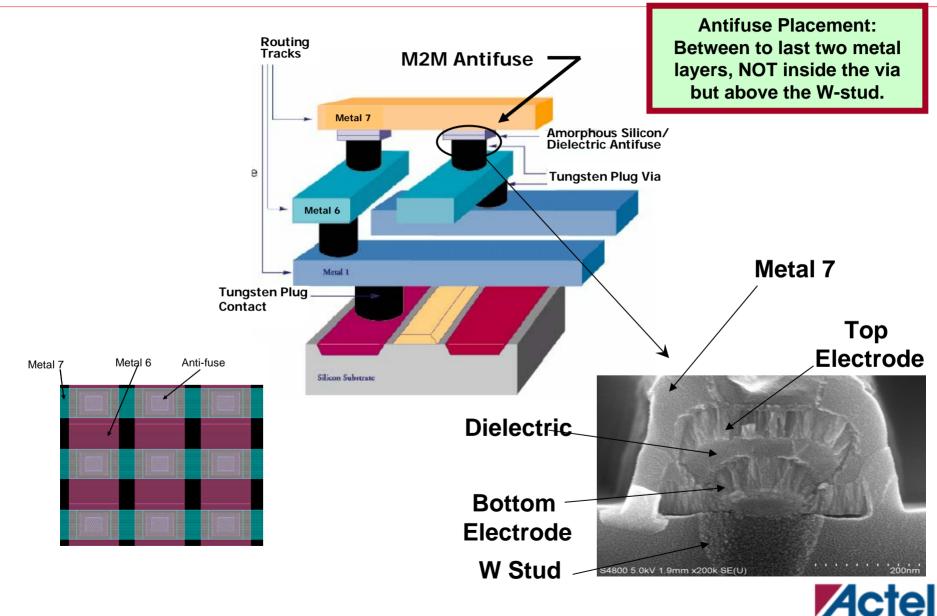

# Metal-to-Metal Antifuse

# **RHAX250-S Product Profile**

| Device                           | RHAX250-S | ]                                                         |

|----------------------------------|-----------|-----------------------------------------------------------|

| Capacity                         |           | Performance                                               |

| Equivalent System Gates          | 250,000   | 1.5V Core; 3.3V I/0                                       |

| ASIC Gates                       | 30,000    | High-Performance Embedded FIFOs                           |

| Modules                          |           | 350+ MHz System Performance                               |

| Register (R-Cells)               | 1,408     | 500+ MHz Internal Performance                             |

| Combinatorial (C-Cells)          | 2,816     | 700 Mb/s LVDS Capable I/Os                                |

| Flip-Flops (Maximum)             | 2,816     | , co + ib/s E i bo capable 1/cs                           |

| Embedded RAM/FIFO (without EDAC) |           |                                                           |

| Core RAM Blocks                  | 12        |                                                           |

| Core RAM Bits (K = $1,024$ )     | 54 K      |                                                           |

| Clocks Segmentable               |           | Dediction Headness Tennets                                |

| Hardwired                        | 4         | Radiation Hardness Targets                                |

| Routed                           | 4         | TID ≥ 1Mrad(Si)                                           |

| I/O's                            |           | DR Upset > 1E9 rad(Si)/sec                                |

| I/O Banks                        | 8         | SEL Immune                                                |

| User I/O's (Maximum)             | 248       | SEU <sub>REGS</sub> < 1E-10 errors/bit-day (TMR-hardened) |

| I/O Registers                    | 744       | SEU <sub>e-RAM</sub> < 1E-10 errors/bit-day (EDAC)        |

| Package                          |           |                                                           |

| CCGA/LGA                         | -         |                                                           |

| CQFP                             | 208, 352  |                                                           |

#### <u>RHAX FPGA will have the identical form, fit, and function of its RTAX</u> counterpart.

#### Predicted SEU Rates vs. logic level & freq.

|                                     |    |     | Test data ta                   | ken on RT                | AX Produ     | ct            |           |    |         |

|-------------------------------------|----|-----|--------------------------------|--------------------------|--------------|---------------|-----------|----|---------|

|                                     |    |     | Predi                          | icted SEU R              | ates (erro   | rs/bit/day)   | *         |    |         |

|                                     |    |     |                                |                          |              |               |           |    |         |

|                                     |    |     |                                | Signal Fre               | equency      |               |           |    |         |

|                                     |    |     | Levels of<br>Intervening Logic | 15 MHz                   | 37.5 MHz     | 75 MHz        | 150 MHz   | -  | rsening |

|                                     |    |     | 8-Levels                       | 5.31E-09                 | 7.88E-09     | 3.75E-08      | 8-17E-08  | SE | U Rate  |

| (D. 1. 1.11)                        |    |     | 4-Levels                       | 2.01E-09                 | 8.71E-09     | 1.89E-08      | 6.29E-08  |    |         |

| (Probability of<br>Generating an SI |    |     | 0-Levels                       | 6.08E=10                 | 5.14E-09     | 2.84E-08      | 5.84E-08  |    |         |

|                                     |    |     | * assumed radiat               | tion environmer          | t: GEO-min a | nd 100-mil Al | shielding |    |         |

|                                     | Lo | gic |                                |                          |              |               |           |    |         |

|                                     |    |     | Frequency —                    |                          |              |               |           |    |         |

|                                     |    |     |                                | ability of<br>ng an SET) |              |               |           |    |         |

# Impact of SET on error rate depends on circuit design and signal frequency.

Further SEU Enhancements projected in Rad Hard Process using Epi layer

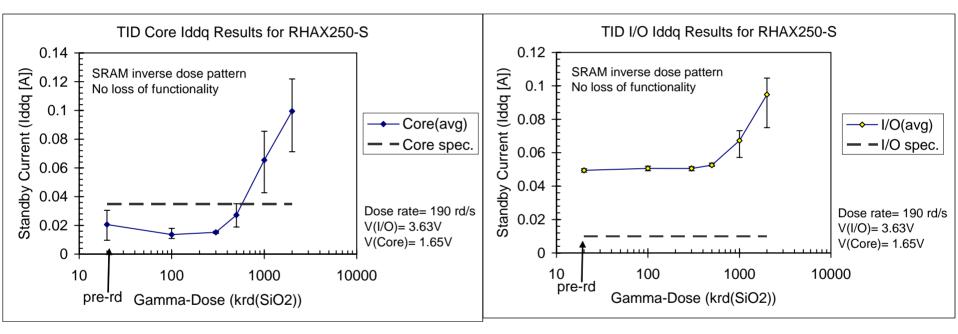

Prototype RHAX250-S FPGA's have yielded functional hardware,

Modules were programmed for total ionizing dose testing.

Circuit elements tested per module:

- 12 blocks of 4Kx1 SRAM (total: 48K)

- 1408-stage DFF register string

- Two 1408-stage logic chains

# RHAX250-S modules remained fully functional throughout testing to 2Mrd(Si0<sub>2</sub>)

TID test results on prototype FPGA's demonstrate improved hardness. Hardening process adjustments are being implemented to further enhance hardness.

- Parts successfully programmed at Actel, with latest QCMON

- Used <u>NASA-Industry Tiger Team</u> Algorithm

- Parts pass all 346 tests at 125 Degrees C except Icca, standby current exceeded specification limit

- Further leakage reduction required for flight parts

| Lot 421 QCMON (346 Total Tests) |                 |                |               |                          |                         |                      |                      |                                    |                       |

|---------------------------------|-----------------|----------------|---------------|--------------------------|-------------------------|----------------------|----------------------|------------------------------------|-----------------------|

| PARTS                           | Contact<br>Test | QCMON<br>Funct | QCMON<br>Hi Z | Input<br>Current<br>High | Input<br>Current<br>Low | Input<br>Pull<br>Ups | Input<br>Pull<br>Dns | Pwr<br>Supply<br>Stdby<br>Currents | Icca Stdby<br>Current |

| Mod # 1                         | Р               | Р              | Р             | Р                        | Р                       | Р                    | Р                    | Р                                  | 20.3mA*               |

| Mod # 2                         | Р               | Р              | Р             | Р                        | Р                       | Р                    | Р                    | Р                                  | 31.5mA*               |

| P=PASS                          |                 | * Note: S      | pec limit i   |                          |                         |                      |                      |                                    |                       |

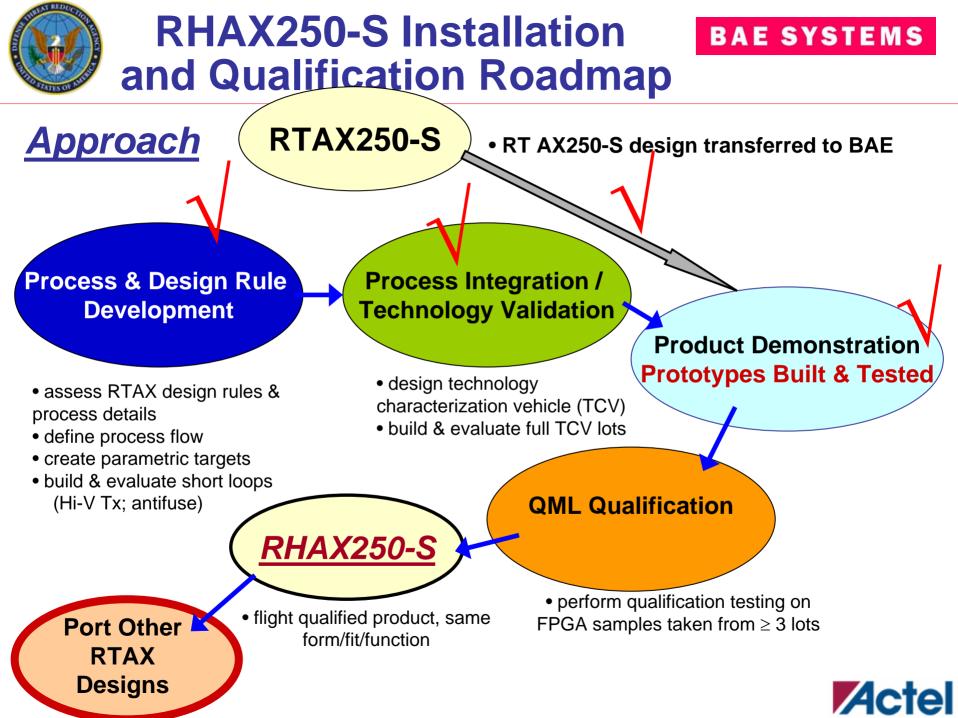

- Build more hardware incorporating identified process enhancements for further leakage reduction

- Subject functional hardware to full battery of reliability and radiation testing

- QML qualify the RHAX process technology

- Begin full RHAX250-S wafer production to supply Actel

- Port additional Actel RTAX FPGA designs onto rad hard process technology at BAE to extend rad hard offerings.

- BAE and Actel are continuing their >12 year collaboration as rad hard FPGA suppliers.

- Next generation rad hard product is being built and tested.

- Total dose test results on RHAX250-S hardware demonstrates improved hardness over RTAX250-S.

- Single-event effects test results on AX250 demonstrates product design's high tolerance.

- Electrical, radiation, and reliability testing is on-going.

- Full flight-qualified production in progress for ONO technology and projected to start M2M technologies in early 2009

# The authors gratefully acknowledge the support for this effort provided by the Defense Threat Reduction Agency under contract DTRA01-03-D-0007 / 0004.